offon哪个是开关键(offon哪个是开关键图片)

我们最常见到的电子元器件是什么。无疑是LED。在我们的生活中它无处不在。比如手机的背光。汽车的头灯。几乎所有的照明也都是LED的了。

当然。对于我们做硬件的“板农”来讲。 哪个板子通上电以后没有俩LED在亮。你心里一定发毛 - 电源短路了?程序挂了?

只要电源灯亮了。心理就踏实了.....3.3V在正常工作。状态指示灯只亮可能还不够。因为它的表情应该非常丰富。不同的节奏可能代表不同的状态。你需要根据其闪烁的节奏来判断系统所处的状态。用过树莓派的同学都知道。在你插上电的那一刻起。树莓派的状态等就各种花式变换。

简单的一颗灯。一颗单色的灯。就能给你提供非常丰富的信息。像不像我们常用的示波器。电压表?

是的。我就是这么看重它的 - LED就是相当于数字逻辑的“示波器”。所以。我在每一个FPGA程序里面(无论多简单的功能)。逻辑体的头4行必定是:

reg [23:0] cnt;

always @(posedge clk_in)

cnt = cnt + 1'b1;

assign hb_led = cnt[23];

为何?看到灯按照我设定的频率闪了。我心理踏实。就像听到了电路的心跳(hb = heart beat:心跳)。知道编译对了。管脚分配对了。时钟是有的...

所以。数字逻辑编程要先植入一个LED灯的程序。

当然。就像程序员学习任何一门语言。必然先打印出"Hello World"一样。FPGA的学习要先从点亮LED开始!

点亮了灯。你也就有了探头。也就能够通过它一窥神秘的FPGA内部的脉搏。

同样。在我们这个学期的“数字电路”学习的系列文章中。我们也先从点亮LED入手。

点亮LED

就像软件编程里的“Hello World”。点灯是FPGA学习的第一步。不要小瞧这么一颗小小的灯。点灯的方式可以有多种。在本节。我们通过4个点灯的程序达到以下的目标:

体验LED的工作原理;了解Verilog代码的结构和基本的语法规范体会HDL语言中的bit和FPGA端口电信号的关系体验FPGA设计从创建工程 –》 输入代码 –》 逻辑综合 –》 分配管脚 –》 生成可下载的JED文件 –》 配置FPGA整个过程(理论知识参见FPGA设计流程)在本实例中。我们以Web IDE(www.stepfpga.com)为例。同样的示例也可以通过Lattice的官方FPGA设计工具Diamond或Intel的官方设计工具quartus_prime来实现。只是要注意这些工具的使用方法和管脚的正确分配。

1. 硬件说明

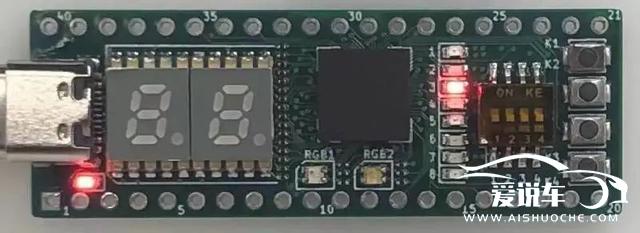

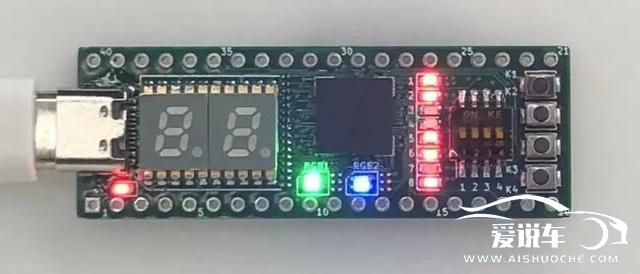

在这个实验中。我们主要用到小脚丫FPGA开发板上的以下几个外设:

板上有8个LED灯。可以选用其中的任何一个做单LED的实验

这是开发板上的8个红色LED。LED1~8信号连接到FPGA的引脚。作为FPGA输出信号控制。当FPGA输出低电平时LED变亮。当FPGA输出高电平时LED熄灭。

板上由2个三色LED(R-红色。G-绿色。B-蓝色)。每个三色灯相当于3个独立的。不同颜色的LED组合成的。如果与三色灯保持一定的观察距离。一个三色灯里的两种以上LED点亮即可组合成其它颜色。在此只是粗略地合成。如果要精确合成不同的颜色。需要精密控制流经R。G。B上每个灯的电流(取决于灯的特性。串联的限流电阻以及控制这些管脚开关的PWM的占空比。这个以后再讲)

这是开发板上的2个三色LED。(R_LED1。 G_LED1。 B_LED1)。 (R_LED2。 G_LED2。 B_LED2)信号连接到FPGA的引脚。作为FPGA输出信号控制。当FPGA输出低电平时。相应的LED变亮。当FPGA输出高电平时LED熄灭。

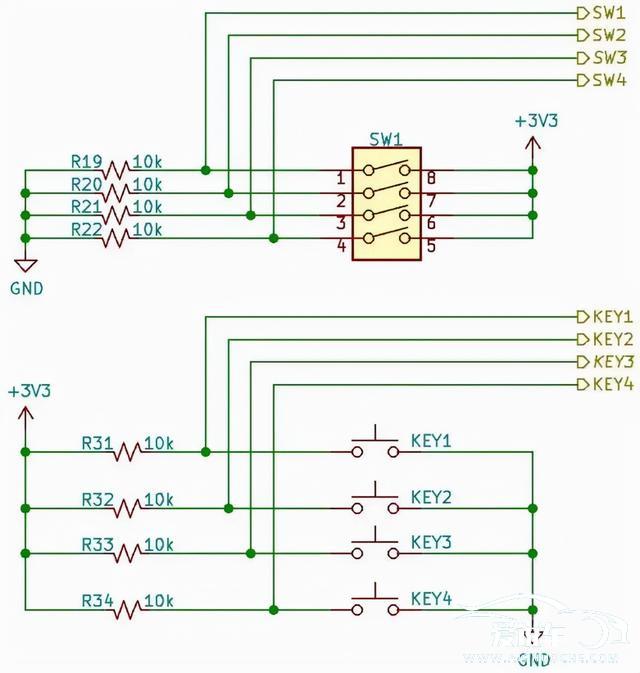

板上有4个按键和4个开关。用做输入控制。按键和开关的使用方式是有区别的。大家可以通过具体的使用来体会

这是开发板上4个按键和4个开关。Key1~4是按键控制信号。SW1~4是开关控制信号。都连接到FPGA的引脚。作为FPGA的输入信号。当按键断开时。FPGA输入为高电平。当按键按下时。FPGA输入为低电平;当开关断开(OFF)时。FPGA输入为低电平。当开关合上(ON)时。FPGA输入为高电平。所以我们可以用开关或者按键来控制LED的亮灭。

2. 点亮一颗LED

根据Web IDE的使用流程介绍。我们先创建一个叫one_led_on_off的工程。并在该工程里面创建一个叫one_led_on.v的代码(代码名字跟工程的名字不需要一致):

module one_led_on(led);

output led;

assign led = 1'b0;

endmodule

这段代码可以说是最简单的一段Verilog程序了。从这段程序中可以看出Verilog语言的基本结构

以module(模块)开始。endmodule结束的一段程序为描述某一项功能的基本单元。类似基于对象编程软件里面的“类”。写一次可以被多次调用。简单的设计可能只需要一个module来包含所有的逻辑功能。复杂的设计可能就需要多个module。它们通过module的端口信号互相连接起来。它们可以并行执行。模块化的好处就是你可以直接调用别人封装好的module来使用;每个模块都有其名字。建议用贴切含义的英文来命名(比如本示例里面的one_led_on)。可读性强。也不会出现莫名其妙的编译错误;每个模块都有用( )包裹起来的端口 - 跟其它模块或FPGA的外围电路打交道的输入输出信号。在本示例只用了一个端口led。因此( )中只有一个端口的名字;对每一个端口的属性进行定义 - 是输入还是输出。如果是内部信号。它们是导线wire类型。还是存储器reg类型?在这里只用了一个输出端口led。对其属性“output”进行了定义。指定其为输出信号;定义完端口。就开始逻辑的主体。在这里也很简单。只是让led这个管脚信号为低电平。使用连续赋值的assign语句 - assign led = 1'b0。 1’b0表示为一位的数字。而且值为“0”。从电路结构角度讲。每个连续赋值语句对应一个子模块。其左侧的变量表示为电路的输出。右侧的逻辑表达式为电路需要执行的逻辑操作。点击Web IDE的第二个功能键“逻辑综合”。系统会自动将你写好的Verilog代码进行综合。如果没有语法错误。则给你一个Success的信息。你就可以走到下一步 - “管脚分配”了。我们的Web IDE会根据你写好的module自动提取输入输出管脚的名字。你只要使用鼠标。通过图形化的界面将这些module里的端口信号的名字映射到相应的管脚上即可。在这里我们将led映射到板子上的第三个led。鼠标指向led3。其右侧会弹出一个向下的箭头。点击该箭头。就可以看到led的名字了(如果多个端口还没有分配管脚。这些未分配的端口信号的名字会出现在列表中)。选中led。完成映射。

在“管脚分配”里将第三颗LED配置为亮 (ON)。分配了管脚的地方会亮起来

点击“FPGA映射”。系统会自动根据你分配好的管脚执行。生成JED文件。如果没有错误。会列出一堆的信息后。告诉你生成了jed的文件。在这段信息中也会有详细的资源使用报告。这些资源报告的信息也是很重要的。为完成同样一个功能。不同的人写出来的逻辑占用的资源也是不同的。

这时候您可以点击“文件下载”。选择第二个按钮“下载JED文件”。鼠标右键 –》另存为。。。指向到StepFPGA的盘即可完成对FPGA的下载编程。

配置到FPGA以后的效果。第三颗LED灯亮

3. 点亮多颗LED

正如上所述。我们小脚丫FPGA板上有8颗LED和2颗3色LED。总计8+6=14颗。我们通过逻辑让某些灯亮。某些灯灭。看看代码如何写。实际的效果如何?比如:

8颗LED灯中的1。2。5。6。8亮第一个RGB灯中的绿色灯亮第二个RGB灯中的蓝色灯亮其它灯都关掉代码如下:

module one_led_on(led。 led_r1。 led_g1。 led_b1。 led_r2。 led_g2。 led_b2);

output [8:1] led; // define 8 led signals to be output

output led_r1。 led_g1。 led_b1;

output led_r2。 led_g2。 led_b2;

assign led_r1=1'b1; // set signal of this pin = 1 to turn off the led connected to this pin

assign led_g1=1'b0; // make the green led on

assign led_b1=1'b1;

assign led_r2=1'b1;

assign led_g2=1'b1;

assign led_b2=1'b0; // make the blue led on

assign led = 8'b01001100; // set bit 8。 6。 5。 2。 1 = 0 to make led 8。 6。 5。 2。 1 on

endmodule

Verilog语法说明:

此模块增加了一些管脚。需要对每一个管脚做端口说明(目前都还是”输出“的属性)。并对每个管脚的信号电平进行赋值。对应于“亮”的LED赋值为0。 对应于“灭”的LED赋值为1。每一个连续赋值语句对应于一个电路结构。这些电路都是并行执行的。因此语句的顺序不会影响到最终的综合结果。这是与单片机的程序(顺序执行)不同的地方;8个LED可以分别写在端口里。并逐个赋值。也可以以8位位宽的向量方式来定义。在端口了只需要写一个led的名字即可。在端口定义的部分指定有多少个位 - [8:1] led。 为8位。名字分别外led[8] (对应于LED8)….led[1](对应于LED1);一个好的代码。要对一些重要的信息给出“注释”说明。单行注释可以用//的方式。//后面的部分为注释内容。多行注释(又被称为块注释)以两个字符/* 开始。并以*/结束。其中的多行内容都会被认为是注释内容。在仿真或综合的时候被忽略掉。为增强可读性和兼容性。注释部分最好用英文来写。管脚分配图如下:

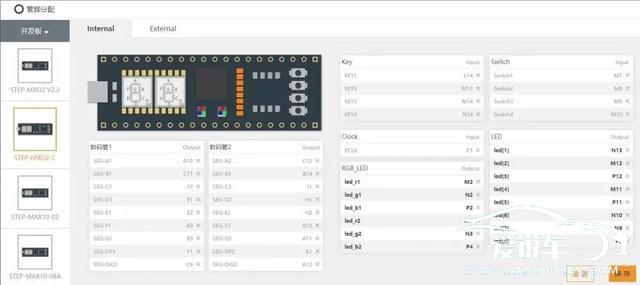

8颗单色的LED和两颗的3色LED都被分配了管脚

下载到小脚丫FPGA板子上。实际的效果验证:

将JED文件下载到FPGA板子以后的效果

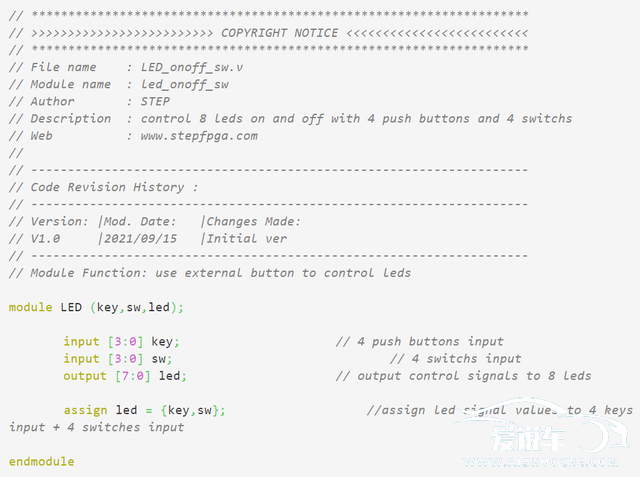

4. 开关控制LED的亮和灭

Verilog语法说明:

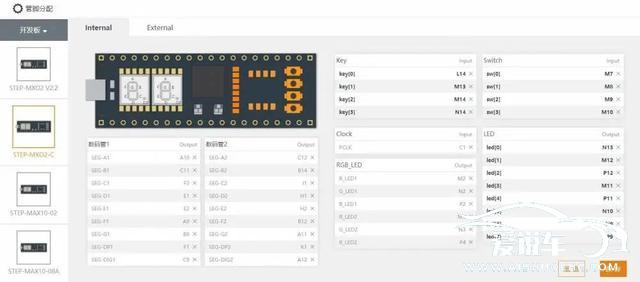

规范的代码需要对该模块进行充分的注释说明。因此在此段代码的前部。我们增加了更详细的信息 - 文件名。作者。日期。简单的描述。版本号等等。这些信息对于代码的管理和控制是非常有必要的。因此要养成良好的习惯。我们硬禾实战营在学员的培训过程中专门制定了一套代码规范 - 硬禾实战营FPGA代码规范;虽然使用的输入输出端口多了。代码却变简单了。这是因为用到的信号都是可以以向量的方式进行定义和操作的。比如4个按键。4个开关和8个LED。只有三种不同性质的端口。而且这三种端口之间的逻辑关系非常清晰;最后的assign语句中用到了拼接符{ }。key的4位和sw的4位拼接在一起。映射到led的8位上。管脚分配如下:

将模块端口的16个信号分别分配给8个LED和4个按键。4个开关

用开关和按键可以控制LED的on/Off。 正常开关和按键的状态都为高电平。8个LED都处于灭的状态。改变开关和按键的装填可以让LED亮起来。按键。开关和LED一一对应。

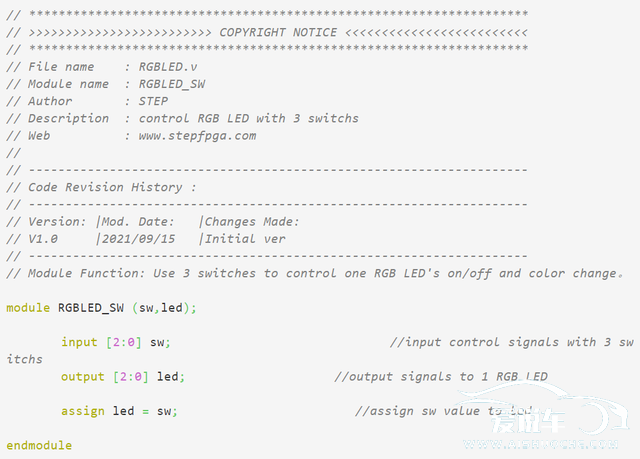

5. 开关控制LED的颜色组合

从逻辑的角度。这段代码跟第4节的代码没什么区别。用了一个三色LED灯代替8个单色的灯。目的是为了让大家通过实际的效果体会一下三色灯的颜色搭配。

代码见下:

分配一下管脚:

一颗RGB和3个开关被映射到端口信号上

6. 小结

通过4段代码。我们体验了对LED的开关控制以及最基本的Verilog语法要求和代码构成。以及开关和按键的控制差异。这为后期的输入输出控制。状态输出展示打下了基础。